Когда процессор "гуляет"

Систему притормаживают не только задержки в «недрах» памяти. Любое обращение к ОЗУ сопровождается передачей в контроллер памяти большой группы сигналов, осложняющих схемотехнику. Громоздкость сигнального аппарата повышает латентность подготовительного периода цикла обмена данными. О чем идет речь?

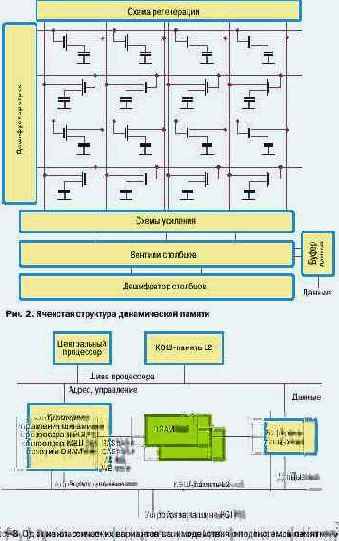

В DRAM каждую ячейку можно отыскать по ее адресным координатам, оформленным в строки и столбцы (рис. 2 ).

Все ячейки выводятся на общую числовую шину. Выбор соответствующего адреса строки и столбца позволяет определить место ячейки. Содержимое нескольких ячеек, объединенных на выходе, образует информационную группу — байт, или слово, и следует на шину данных памяти. Разрядность внешней шины данных памяти позволяет повысить ее пропускную способность. Вместе с тем рост быстродействия памяти не возымеет никакого эффекта, если она не способна работать с малыми временными задержками.

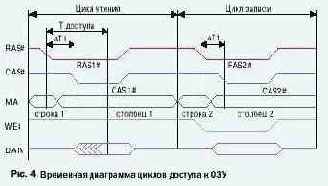

Адрес памяти содержит сведения для выбора: байта, банка, строки и столбца. Он поступает в один из портов контроллера ОЗУ, трансформируется в два адреса — строки и столбца, которые по шине MA попадают в DRAM (рис. 3) с некоторым промежутком времени (ΔT1 на рис. 4).

Контроллер памяти оснащен портом для обмена данными с процессором и еще одним портом — для обмена с устройствами ввода вывода на системной шине. В современных чипсетах первый порт называется «северным», а другой «южным». С таким же успехом порт AGP может быть назван «западным»… Поскольку «соискателей» для обмена много, на входе подсистемы имеется арбитр. Этот «строгий привратник» подключает к памяти устройства в соответствии с приоритетами. На этот процесс также уходит время.

Шина между процессором и контроллером ОЗУ —